# **Features**

- User programmable copy protection IC

- 32 Kbits EEPROM, Retention(10 years)

- Erase/Write Endurance: 100K@25°C

- Support AES128 encryption and decryption SHA256/AES128 Authentication

- User ID, User Serial, MIDR, RVC

- 3.3V Operation Voltage, I2C I/F

- Built- in Power on Reset and 8 MHz OSC.

- Active, Sleep Power Mode

# **Applications**

- Print cartridge, GPS, Navigation

- Mobile Device, IPC, CCTV, DVD

- Set-Top Boxes (STBs), Etc.

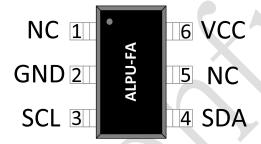

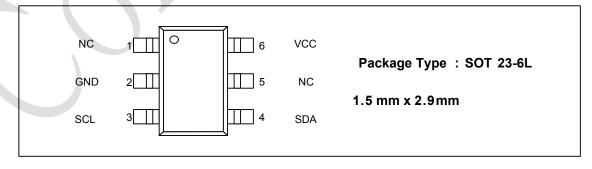

# Pin Configuration

<SOT-23-6L Package>

• SOP8 packages will be available.

# **General Description**

The GEN -FA has 32 Kbits EEPROM. A configurat ion data and user data can be saved at the EEPRO M. The data is protected by password and encryptio n. The GEN has SHA-256 core. SHA-256 is used f or a authentication. It is a slave device that always

operates with MCU through the serial bus. The GEN has internal 8 MHz clock. When MCU does not access the GEN for a defined time, The GEN goes to sleep mode. The 8MHz OSC does not oscillate for sleep mode.

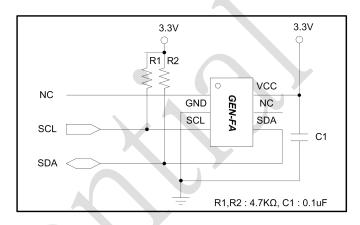

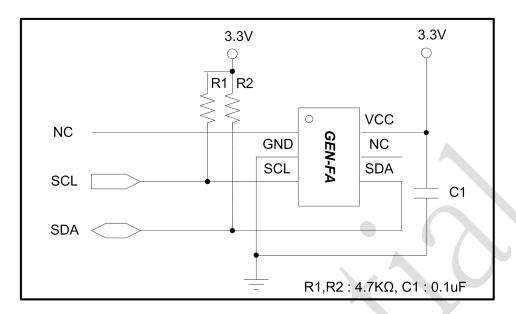

# **Typical Operation Circuit**

< SOT-23-6L Package Type >

SCL and SDA is open drain. SDA is bi-directional port.

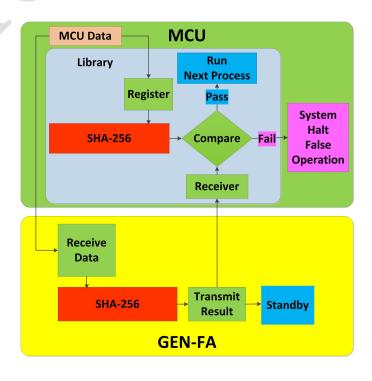

# **SHA256** Authentication Flow

# Contents

| <u>1. Overview</u>            | 3  |

|-------------------------------|----|

| 2. I/O Port                   | 5  |

| 3. Clock Management           | 7  |

| 4. Power Mode                 | 7  |

| 5. Initialization             | 8  |

| 6. Encryption                 | 9  |

| 7. EEPROM                     | 13 |

| 3. Communication Interface    | 13 |

| 9. Electrical Characteristic  | 16 |

| 0. Typical Operation Circuit  | 18 |

| 1. Package Information        | 19 |

| 2. Datasheet Revision History | 20 |

### 1. Overview

The GEN-FA has 32 Kbits EEPROM. A configuration data and user data can be s aved at the EEPROM. The data is protected by password and encryption. The GEN has SHA-256 core. SHA-256 is used for a authentication. It is a slave device that always operates with MCU through the serial bus. The GEN has internal 8 MHz cl ock. When MCU does not access the GEN for a defined time, The GEN goes to sleep mode. The 8MHz OSC does not oscillate for sleep mode.

#### 1.1. Features

### 1.1.1 Security

- User programmable copy protection IC

- 32 Kbits EEPROM, Retention(10 years)

- Erase/Write Endurance: 100K

- Standard AES-128 encryption and decryption

- SHA-256/AES-128 Authentication

- User ID, User Serial, MIDR, RVC

- 3.3V Operation Voltage, I2C I/F

- Built- in Power on Reset and 8 MHz OSC.

- Active, Sleep Power Mode

#### 1.1.2 Memories

- 32 Kbits EEPROM

- Configuration Data Region: 2.56 Kbits

- User Data Region : 30.208 Kbits

#### 1.1.3 Peripheral Features

• IIC serial interface, Supporting up to 400 kbps

#### 1.1.4 Special Features

- Built in Power-on-Reset

- Built in 8MHz selectable OSC

- Two Power Modes: Active, Sleep

# 1.1.5 Operating Voltages

• 3.3V Operation Voltage

## 1.1.6 Package

• SOT23-6L

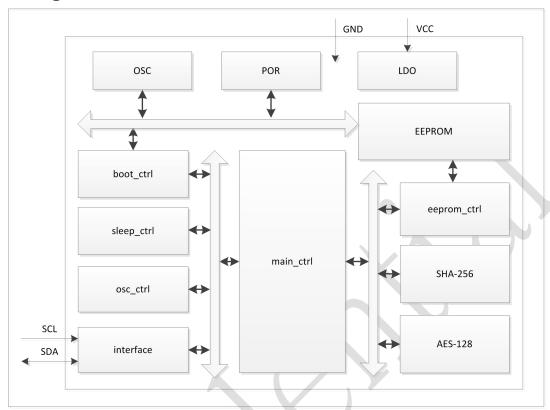

# 1.2. Block Diagram

Figure 1-1. Block Diagram

GEN-FA consists of analog blocks (OSC, POR and LDO) and a memory block and digital logic ones. The boot control block manages the signals of analog blocks. An d the main control block manages the communications between the digital blocks th rough two buses.

# 1.3. Pin Configurations

Figure 1-2. GEN-FA Pin Configuration of SOT23-6L

www.neowine.com 4/18 GEN-FA Datasheet Ver 1.0

# 1.4. Pin Descriptions

Table 1-1. GEN-FA Pin Description of SOT-23-6L

| Pin Num | Pin Name | Description                                   | Remark |

|---------|----------|-----------------------------------------------|--------|

| 1       | NC       | None Connected                                |        |

| 2       | GND      | Ground                                        |        |

| 3       | SCL      | IIC Serial Clock input pin. CMOS Input        |        |

| 4       | SDA      | IIC Serial Data, CMOS Input / Open-Drain Outp |        |

| 4       | SDA      | ut bi-directional I/O                         |        |

| 5       | NC       | None Connected                                |        |

| 6       | VCC (1)  | Digital supply voltage                        |        |

Note (1) The GEN-FA operation voltage is supported by 3.3V

# 2. I/O Port

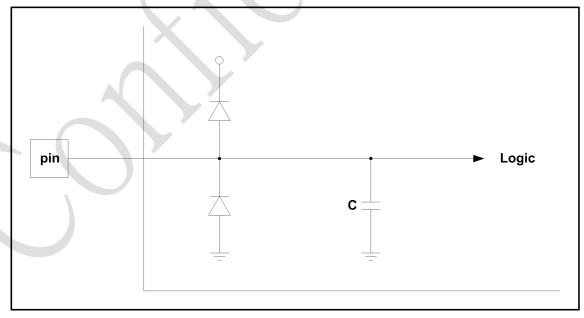

## 2.1 ESD protection circuit

ESD protection circuit for the whole chip is achieved as shown in Figure 2-1. It can be protected the chip against two widely used industry standard ESD test models: Human Body Model (HBM) and Machine Model (MM). Both of these models test each pin against every other pin and/or a power/ground supply using a positive and a negative pulse.

Figure 2-1. ESD protection circuit

# 2.2 I/O type

GEN-FA has I/O types as shown in Table2-1.

www.neowine.com 5/18 GEN-FA Datasheet Ver 1.0

Table 2-1. I/O Types

| Direction         | Name | Description                      |

|-------------------|------|----------------------------------|

|                   | VCC  | Digital supply voltage           |

|                   | GND  | Ground                           |

| Bi-direction Port | SDA  | IIC Serial Data bi-direction pin |

| Input Port        | SCL  | IIC Serial Clock input pin       |

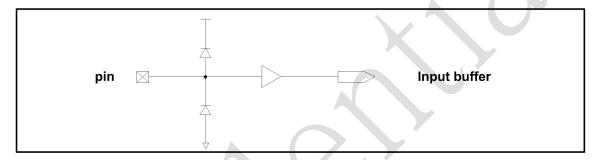

## 2.2.1 Input Port (SCL)

The Input cell is an input buffer with CMOS input.

Figure 2-2. Input port Schematic

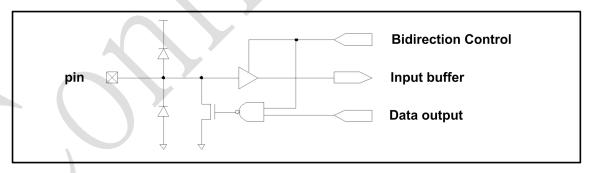

# 2.2.3 Bi-direction Port (SDA)

This cell is a bidirectional buffer with CMOS input and 2mA n-channel open drain output.

Figure 2-4. Bi-direction port Schematic

www.neowine.com 6/18 GEN-FA Datasheet Ver 1.0

# 3. Clock Management

#### 3.1 Internal clock

All Inner blocks use internal OSC clock. EEPROM can select OSC clock between 4 MHz and 8MHz. Internal OSC clock is approximately 8MHz shown in Table3-1.

Table 3-1. Internal OSC parameters (Ta = 25°C)

| PARAMETER          | SYMBOL | CONDITION   | Min | Тур | Max | Unit |

|--------------------|--------|-------------|-----|-----|-----|------|

| Frequency          | f8m    |             | 7   | 8   | 9   | MHz  |

| Frequency Variatio | Δf8m   | -40≤Ta≤80°C | - 0 | - ( | ±10 | %    |

| n                  |        |             |     |     |     |      |

| Duty Cycle         | Dmax   |             | 48  | 50  | 52  | %    |

#### 3.1.1 Clock on/off

Internal OSC clock can be turned on or off. If GEN-FA is in the condition of Slee p-mode, then internal OSC clock is turned off to save the power.

Here is the condition to enter the Sleep-mode. SCL and SDA pins both stay high and all functions are disabled specific time duration. This time can be from 4.096m s to 33 seconds in a 4.096ms time step. MCU can change this time duration with c hanging related register values. When the conditions above are not met it wakes u p to active-mode. (Refer to chapter 4. Power Mode)

#### 4. Power Mode

GEN-FA supports the power saving mode called Sleep-mode in which internal oscillator is off.

#### 4.1 Condition of entering Sleep-mode

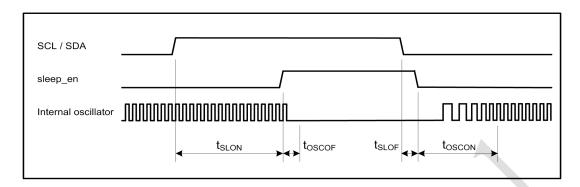

Here is the condition to enter the Sleep-mode. SCL and SDA pins both stay high and all functions are disabled for specific time duration. This time can be from 4.0 96ms to 33 seconds in a 4.096ms time step. MCU can change this time duration with changing related register values. (Refer to Figure 4-1)

www.neowine.com 7/18 GEN-FA Datasheet Ver 1.0

Figure 4-1. Sleep-mode Waveform

SCL/SDA: IIC signal

sleep\_en: internal sleep-enable signal

Internal oscillator: 8MHz oscillator for internal logic

Table 4-1. Sleep-mode Waveform Parameters

| Parameter           | Symbol            | MIN   | TYP | MAX   | Unit |

|---------------------|-------------------|-------|-----|-------|------|

| Sleep-mode On Time  | t <sub>SLON</sub> | 4.096 |     | 33000 | ms   |

| Sleep-mode Off Time | t <sub>SLOF</sub> |       |     | 10    | ns   |

| OSC On Time         | toscon            |       |     | 5     | us   |

| OSC Off Time        | toscof            |       |     | 10    | ns   |

# 4.2 Condition of exiting Sleep-mode

When the conditions are not met it wakes up to active-mode; Either SCL or SDA line goes down to low.

## 5. Initialization

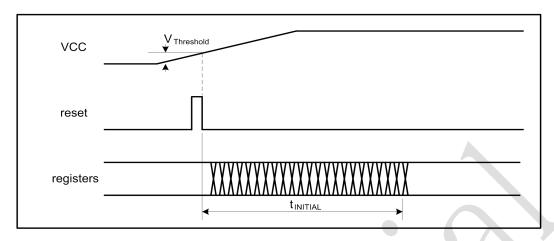

GEN-FA has an internal POR (Power-on-Reset) circuit. When system power turns on GEN-FA's POR resets its own system. During reset time, all internal registers of GEN-FA are configured as their initial values. (Refer to chapter 9. Electrical Characteristic)

#### 5.1 Start-up Waveform

After RESET, internal registers in GEN-FA need  $t_{\rm INITIAL}$  time period to initialize all registers. After  $t_{\rm INITIAL}$  time period GEN-FA's sleep time value can be changed by MCU. After Power On RESET the sleep time value is 33 seconds.

www.neowine.com 8/18 GEN-FA Datasheet Ver 1.0

Figure 5-1. Start-up Waveform

VCC: 3.3V Supplied Power

reset : internal Power-on-Reset signal

registers: internal registers for initialization

Table 5-1. Start-up Timing Parameters

| Parameter         | Symbol               | MIN | TYP | MAX | Unit |

|-------------------|----------------------|-----|-----|-----|------|

| Threshold Voltage | $V_{Threshold}$      | 1.1 | 1.2 | 1.3 | V    |

| Initial Time      | t <sub>INITIAL</sub> |     |     | 14  | ms   |

VCC information (Refer to chapter 10. Electrical Characteristic)

## 5.2 Internal Power-on-Reset

A Power-on-Reset (POR) pulse is generated by an On-chip detection circuit. The detection level is defined in Table5-1. The POR is activated whenever VCC is below the detection level (threshold voltage). The POR circuit ensures that the device is reset from Power-on. Reaching the POR threshold voltage invokes the delay counter, which determines how long the device is kept in RESET after VCC rise.

# 6. EEPROM

GEN-FA has 32 Kbits EEPROM memory. The memory write and read instructions are achieved through IIC interface. Refer to Application Notes

# 7. Communication Interface

## 7.1 IIC interface (Two Wire Interface)

www.neowine.com 9/18 GEN-FA Datasheet Ver 1.0

The IIC Interface is ideally suited for typical microcontroller applications. The IIC protocol allows the systems designer to interconnect up to 128 different devices u sing only two bus lines, one for clock (SCL) and one for data (SDA). The only ext ernal hardware needed to implement the bus is a single pull-up resistor for each of the TWI bus lines. All devices connected to the bus have individual addresses.

GEN-FA operates as a slave device on the IIC bus. IIC interface on GEN-FA is c ompatible with Phillips Format, supporting up to 400 Kbps

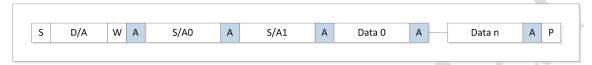

#### 7.1.1 Write Packet Structure

Figure 7-1. Write Packet Structure

S: Start

D/A: Device Address (Slave Address) 7bit

W: Device Address Write bit (0)

A: Acknowledge

S/A0, S/A1: Sub Address, S/A0(MSB 8bits of 16bits Address), S/A1(LSB 8bits of 16bits Address)

Data 0~n: Write Data

P: Stop

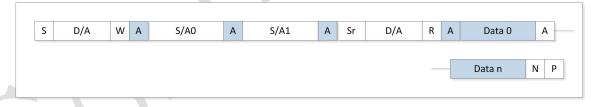

#### 7.1.2 Read Packet Structure

Figure 7-2. Read Packet Structure

S: Start

D/A: Device Address (Slave Address) 7bit

W: Device Address Write bit (0)

A: Acknowledge

S/A0,S/A1: Sub Address, S/A0(MSB 8bits of 16bits Address), S/A1(LSB 8bits of 16bits Address)

Sr: Repeated Start (Non-Stop)

R: Device Address Read bit (1)

www.neowine.com 10/18 GEN-FA Datasheet Ver 1.0

Data 0~n: Read Data N : No Acknowledge

P: Stop

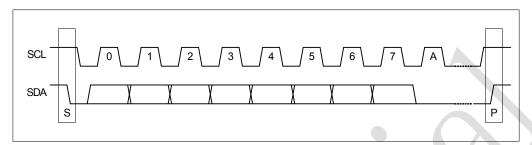

## 7.1.3 Waveform

Figure 7-3. IIC waveform

## 7.1.4 Definition of timing

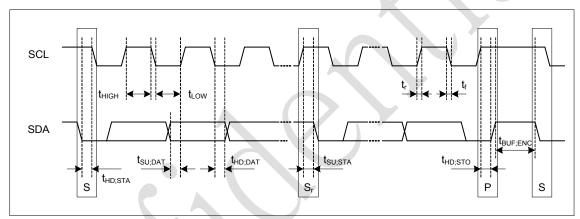

Figure 7-4. Definition of timing

Table 7-1. IIC Timing Parameters

|                              |                       | Standard-Mod |     | Fast-Mode |     |      |

|------------------------------|-----------------------|--------------|-----|-----------|-----|------|

| Parameter                    | Symbol                | •            | 9   |           |     | Unit |

|                              |                       | MIN          | MAX | MIN       | MAX |      |

| SCL clock frequency          | $f_{SCL}$             | 0            | 100 | 0         | 400 | KHz  |

| Hold time (repeated) START   | t <sub>HD;STA</sub>   | 4.0          | _   | 0.6       | _   | us   |

| condition.                   |                       |              |     |           |     |      |

| LOW period of the SCL clock  | $t_{ m LOW}$          | 4.7          | _   | 1.3       | _   | us   |

| HIGH period of the SCL clock | t <sub>HIGH</sub>     | 4.0          | _   | 0.6       | _   | us   |

| Setup time for repeated STA  | t <sub>SU;STA</sub>   | 4.7          | _   | 0.6       | _   | us   |

| RT condition                 |                       |              |     |           |     |      |

| Data hold time               | t <sub>HD;DAT</sub>   | 5.0          | _   | _         | _   | us   |

| Data setup time              | $t_{\mathrm{SU;DAT}}$ | 250          | _   | 100       | _   | ns   |

www.neowine.com 11/18 GEN-FA Datasheet Ver 1.0

| Rising time of both SDA and  | t <sub>r</sub>           | -   | 1000 | 20  | 300 | ns |

|------------------------------|--------------------------|-----|------|-----|-----|----|

| SCL signals                  |                          |     |      |     |     |    |

| Falling time of both SDA and | t <sub>f</sub>           | _   | 300  | 20  | 300 | ns |

| SCL signals                  |                          |     |      |     |     |    |

| Setup time of STOP condition | t <sub>SU;STO</sub>      | 4.0 | 1    | 0.6 | _   | us |

| Bus free time between STOP   | t <sub>BUF;ENC</sub> (1) | 1   | 1    | 1   | _   | ms |

| and START condition          |                          |     |      |     |     |    |

Note (1) It need for encryption processing time.

www.neowine.com 12/18 GEN-FA Datasheet Ver 1.0

# 8. Electrical Characteristic

## 8.1 Absolute Maximum Ratings

Table 8-1. Absolute Maximum Ratings

| Parameter              | Min  | Max | Units |

|------------------------|------|-----|-------|

| Supply Voltage         | 2.7  | 6.0 | V     |

| Storage Temperature    | -35  | 120 | °C    |

| ESD Susceptibility     | 2000 |     | V     |

| DC Current VCC and GND |      | 3   | mA    |

Note. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied.

## 8.2 Recommended Operating Conditions

Table 8-2. Recommended Operation Conditions

| Parameter             | Min | Max | Units |

|-----------------------|-----|-----|-------|

| Operating Temperature | -30 | 80  | °C    |

| Operating Voltage     | 3.0 | 3.6 | V     |

# 8.3 DC Characteristics

Table 8-3. DC Specifications 3.3V I/O

| Symbol           | Parameter           | Condition             | Min  | Тур | Max  |

|------------------|---------------------|-----------------------|------|-----|------|

| $V_{IL}$         | Input Low Voltage   |                       |      |     | 0.8V |

| V <sub>IH</sub>  | Input High Voltage  |                       | 2.0V |     |      |

| $I_{\mathrm{I}}$ | Input Leakage       | VCC = MIN             |      |     | 1uA  |

|                  | Current             | $V_{IN}$ =GND or 3.6V |      |     |      |

| V <sub>OL</sub>  | Output Low Voltage  | $I_{OL} = 2mA$        |      |     | 0.4V |

| V <sub>OH</sub>  | Output High Voltage | $I_{OH} = 2mA$        | 2.4V |     | 3.6V |

Table 8-4. Supply Current

| Symbol                              | Parameter           | Condition             | Min                 | Тур                  | Max |

|-------------------------------------|---------------------|-----------------------|---------------------|----------------------|-----|

| т                                   | VCC Complex Comment | Active 8MHz, VCC=3.3V |                     | 500uA <sup>(1)</sup> |     |

| I <sub>VCC</sub> VCC Supply Current | Sleep mode          |                       | 90uA <sup>(2)</sup> |                      |     |

www.neowine.com 13/18 GEN-FA Datasheet Ver 1.0

Note (1) TBD. (2) TBD.

## 8.4 Internal IP

Table 8-5. Internal Oscillator (Ta = 25°C)

| Symbol           | Parameter           | Condition   | Min  | Тур  | Max   |

|------------------|---------------------|-------------|------|------|-------|

| fOSC             | Switching Frequency |             | 7MHz | 8MHz | 9MHz  |

| $\Delta f_{OSC}$ | Frequency Variation | -40≤Ta≤80°C | _    |      | ±10 % |

| Dmax             | Duty Cycle          |             | 48%  | 50%  | 52%   |

Note  $^{(1)}$  When the ring voltage is 3.3V (typical), CMOS voltage level and LVTTL v oltage level are the same.

Table 8-6. Power-on-Reset

| Symbol             | Parameter             | Condition | Min   | Тур  | Max    |

|--------------------|-----------------------|-----------|-------|------|--------|

| Vt                 | Threshold Voltage     | A         | 1.1 V | 1.2V | 1.3V   |

| t <sub>RINIT</sub> | Register Initial time |           |       |      | 160 us |

Table 8-7. EEPROM cell

| Symbol              | Parameter           | Condition | Min   | Тур  | Max      |

|---------------------|---------------------|-----------|-------|------|----------|

| I <sub>VDD_R</sub>  | Read Current VDD    |           |       |      | 128uA    |

|                     |                     |           |       |      | (32bits) |

| $I_{VPP\_R}$        | Read Current VPP    |           |       |      | 704uA    |

|                     |                     |           |       |      | (32bits) |

| $I_{VDD\_P}$        | Program Current VDD |           |       |      | <1uA     |

| I <sub>VPP_P</sub>  | Program Current VPP |           |       |      | 600uA    |

|                     |                     |           |       |      | (for 1bi |

|                     |                     |           |       |      | t)       |

| I <sub>VDD_SB</sub> | Standby Current VDD |           |       |      | <1uA     |

| I <sub>VPP_SB</sub> | Standby Current VPP |           |       |      | <1uA     |

| $V_{PP}$            | Program VPP Voltage |           | 6.25V | 6.5V | 6.75V    |

Note. No active current at sleep mode thus  $I_{VDD\_SB \text{ and}} I_{VPP\_SB}$  is dependent on device leakage current.

# 9. Typical Operation Circuit

www.neowine.com 14/18 GEN-FA Datasheet Ver 1.0

Figure 9-1. GEN-FA Operation Circuit

R1, R2 :  $2K \sim 10K$  ohm (TYP. 4.7K ohm)

C1: 0.1uF

www.neowine.com 15/18 GEN-FA Datasheet Ver 1.0

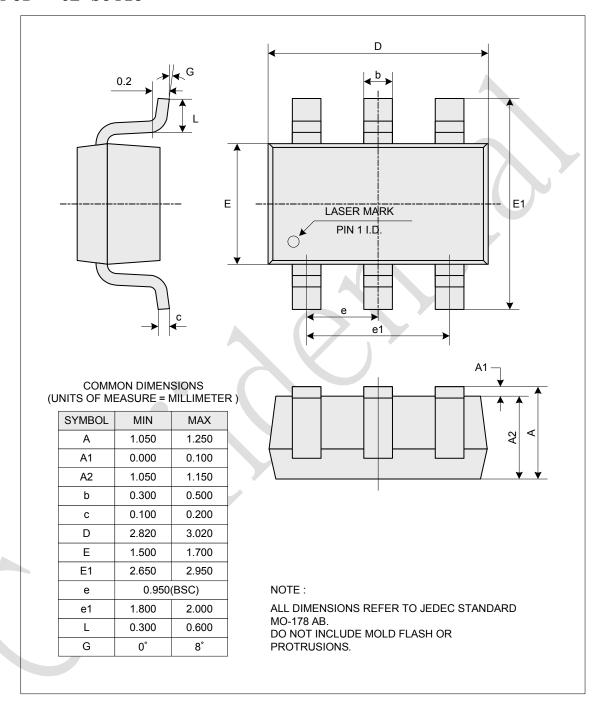

# 10. Package Information

## 10.1 POD - 6L-SOT23

Figure 10-1. 6L-SOT23 Package Outline Dimension

www.neowine.com 16/18 GEN-FA Datasheet Ver 1.0

# 11. Datasheet Revision History

11.1 Ver 1.0 (2015/10/28)

- Initial version release.

www.neowine.com 17/18 GEN-FA Datasheet Ver 1.0

NEOWINE Co., Ltd.

### http://www.neowine.com

## Headquarters

#401, 182, Pangyoyeok-ro, Bundang-gu, Seongnam-si, Gyeonggi-do,

Korea 463-400

Tel: 82-31-706-8484 Fax: 82-31-706-8485

info@neowine.com

## China Office

上海:徐汇区中山西路1788弄58号302室

深圳:宝安区宝安大道4018号华丰国际商务大厦806

Tel: 86-21-6278-2288(ext 221) Fax: 86-21-6278-3723

alpu-china@neowine.com

www.neowine.com 18/18 GEN-FA Datasheet Ver 1.0